SHARC Floating Point DSP from Analog Devices

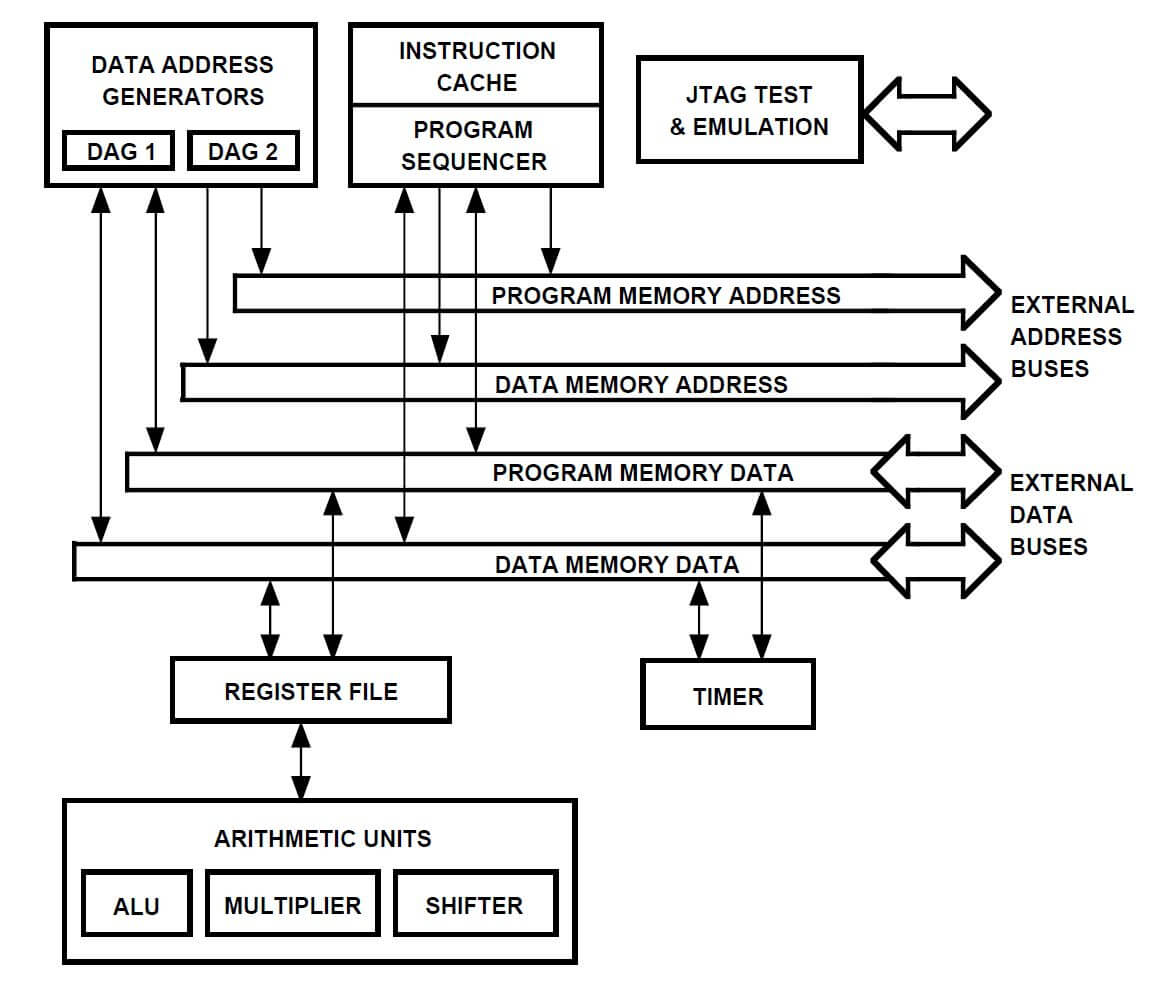

Analog Devices SHARC are 32-Bit floating-point digital signal processors that came to life in the early 1990s. Today, the 6th generation SHARC processors is available. Originally, SHARC (Super Harvard ARChitecture) were pure signal processing CPUs. There were two devices, both virtually identical, with the ADSP-21010 clockes at up to 12.5 MHz whereas the ADSP-21020 allowed clock rates of up to 30 MHz. The core architecture remained virtually unchanged across the generations.

Analog Devices SHARC are 32-Bit floating-point digital signal processors that came to life in the early 1990s. Today, the 6th generation SHARC processors is available. Originally, SHARC (Super Harvard ARChitecture) were pure signal processing CPUs. There were two devices, both virtually identical, with the ADSP-21010 clockes at up to 12.5 MHz whereas the ADSP-21020 allowed clock rates of up to 30 MHz. The core architecture remained virtually unchanged across the generations.

The second generation SHARC (ADSP-21060, ADSP-21061(L), ADSP-21062 and the low-cost ADSP-21065) received internal dual-port memory and high-performance interfaces (SPORT, LinkPort). Using the LinkPorts, 2- and 3-dimensional topologies became feasible, somewhat like the Transputers were able to realize. The fastest devices of the second generation SHARCs allowed clock rate of up to 66 MHz achieving a sustained performance of up to 132 MFLOPs.

SHARC processors of the third generation (ADSP-21160, ADSP-21161) added a SIMD unit (Single Instruction Multiple Data) which allowed significant enhancements of calculations of FIR filters and FFTs. At the same time, clock rates went up to a maximum of 100MHz.

LinkPorts were discarded in the forth generation of SHARC (ADSP-2126x, ADSP-2136x) while a much more flexible I/O concept was implemented reducing CPU load through a large number of DMA channels. Since SHARC prozessors had made it big into audio applications, an S/PDIF interface and numerous audio related algorithms in ROM (AAC, Dolby Surround and many more) were added to the architecture. Clock rates of up to 400MHz and up to 3 MBit on-chip RAM allow for complex algorithms to be executed with no external memory.

5th generations SHARCs (ADSP-214xx) boast up to 5 MBit of on-chip RAM and can be clocked at up to 450 MHz. They also contain a CPU co-processor that can execute FIR or IIR filters or FFTs independent of the core. Though the co-processor is clocked at only half the CPU clock, it significantly relieves the core DSP in certain applications.

The last generation of SHARC processors hit the market place in 2015 (ADSP-2158x, 500MHz max.). For the first time, dual-core SHARCs became available, each of which boasts up to 5MBit of private RAM. Both cores can access external memory and peripherals via the so-called 'System Crossbar'. In addition, SHARC processors are available with an on-chip ARM Cortex-A5 (ADSP-SC58x) which expands I/O capabilies through it PCIe (ADSP-SC589, only), USB, CAN and other industrial interfaces. An extended instruction set was added (64-bit SHARC+) but all devcies remain backward compatible with previous generations of SHARC processors. Here is an feature list of sixth generation SHARC DSP.

All SHARC processors, with the exception of generation 1 devices, are readily available until this date (2017).